Field Programmable Gate Array

Ein FPGA (Akronym für Field Programmable Gate Array) ist ein integrierter Schaltkreis (IC) der Digitaltechnik, in welchen eine logische Schaltung geladen werden kann. Die Bezeichnung kann übersetzt werden als im Feld (also vor Ort, beim Kunden) programmierbare (Logik-)Gatter-Anordnung.

Anders als bei der Programmierung von Computern, Mikrocontrollern oder Steuerungen bezieht sich hier der Begriff Programmierung nicht nur auf die Vorgabe zeitlicher Abläufe, sondern vor allem auch auf die Definition der gewünschten Schaltungsstruktur. Diese wird mittels einer Hardwarebeschreibungssprache formuliert und von einer Erzeugersoftware in eine Konfigurationsdatei übersetzt, welche vorgibt, wie die physischen Elemente im FPGA verschaltet werden sollen. Man spricht daher auch von der Konfiguration des FPGA. Ohne diese hat der Baustein keine Funktion.

FPGAs stellen eine Weiterentwicklung der PLDs dar und kommen in vielen Gebieten der digitalen Elektronik zum Einsatz.

Anwendung

[Bearbeiten | Quelltext bearbeiten]Durch Konfiguration der intern vorhandenen Elemente können in einem FPGA verschiedene Schaltungen und Funktionen realisiert werden. Diese reichen von Schaltungen geringer Komplexität, wie z. B. ein einfacher Synchronzähler oder Interfaces für Digitalbausteine (z. B. Glue Logic), über Speichercontroller und vollständige Mikroprozessoren bis hin zu hochkomplexen Schaltungen wie Systems-on-a-Chip.

FPGAs werden in allen Bereichen der Digitaltechnik eingesetzt, vor allem aber dort, wo es auf schnelle digitale Signalverarbeitung und flexible Änderung der Schaltung ankommt, um beispielsweise nachträgliche Verbesserungen an den implementierten Funktionen vornehmen zu können, ohne dabei direkt die Hardware ändern zu müssen. Ein großes Anwendungsgebiet ist die Erstellung von Prototypen in der ASIC-Entwicklung zum vorherigen Test sowie auch der Bereich Maintenance bzw. Obsoleszenzmanagement, in dem es darum geht, Ersatz für alte, nicht mehr lieferbare digitale Bausteine oder Mikrocontroller vorzuhalten.

Mit der Einführung der FPGAs wurden kompakte, anwenderspezifische Schaltungen in geringen Stückzahlen ermöglicht. Heute gestatten sie die preiswerte und flexible Fertigung komplexer Systeme wie Mobilfunk-Basisstationen als Alternative zur teureren Auftragsfertigung durch Halbleiterhersteller.

Neben den FPGAs existieren auch FPAAs (Field Programmable Analog Array), die nicht nur digitale, sondern vor allem analoge Funktionsblöcke enthalten, die vom Anwender programmiert und verschaltet werden können. Es handelt sich dabei in erster Linie um Filter und HF-Bauelemente.[1]

Aufbau und Struktur

[Bearbeiten | Quelltext bearbeiten]

Die wesensbestimmende Grundstruktur eines FPGA ist ein Feld (engl. Array) aus Basisblöcken mit jeweils einer einfachen programmierbaren Lookup-Tabelle (LUT) und einem 1-Bit-Register (Flipflop). Die LUTs können, je nach Anzahl der verfügbaren Eingänge, jede beliebige n-stellige Binärfunktion realisieren. Die Programmierung der gewünschten Funktion erfolgt durch die Hinterlegung der definierenden Wahrheitstabelle in den SRAM-Zellen der LUT, die Funktionsberechnung durch das Auslesen der durch die Eingänge bestimmten Speicheradresse. Lange Zeit waren LUT-Strukturen mit 4 binären Eingängen üblich. Neuere FPGAs gehen zur Verringerung des Aufwandes an LUT-zu-LUT-Verbindungen zur Realisierung von Funktionen mit mehr Eingängen auf LUTs mit bis zu 6 Eingängen über.

Neben den LUTs ist auf einem FPGA auch die Verschaltung der Komponenten weitgehend frei konfigurierbar. Multiplexer-Strukturen in den Basisblöcken ermöglichen häufig sehr schnelle lokale Signalpfade, zur Einbindung oder Umgehung des Flipflops, zur Rückkopplung von dessen Ausgang, zur Verbindung von Nachbarblöcken und ähnlichem. Für die ferneren Verbindungen liegt zwischen den Basisblöcken ein Gitter aus immensen Busstrukturen, an das Ein- und Ausgänge angeschlossen werden können. Weitere programmierbare Schaltkomponenten in den Kreuzungspunkten des Gitters erlauben die Signalverteilung über den gesamten Chip.

Weitere Komponenten

[Bearbeiten | Quelltext bearbeiten]Weitere oft vorzufindende Elemente von FPGA sind:

- Eingangs-/Ausgangs-Blöcke (engl. IO-Blocks oder IOB) dienen der Kommunikation mit der Außenwelt. Über sie werden die externen Anschlüsse des FPGA mit der internen Schaltmatrix verbunden. Sie können an die jeweilige Anwendung angepasst werden, z. B. kann die Ausgangsspannung für den jeweiligen Standard eingestellt werden (TTL/CMOS usw.). Spezielle IOB-Blöcke mit integrierten Serializern gestatten die Anbindung an Hochgeschwindigkeits-Busse und Double-Data-Rate-(DDR)-Schnittstellen.

- Ein oder mehrere Taktgeneratoren erzeugen, ausgehend von an den Eingängen zur Verfügung gestellten Taktsignalen, alle für die Anwendung benötigten internen Taktsignale. Diese können gegenüber den Eingangstaktsignalen in der Phase verschoben sein und besitzen eine von dem jeweiligen Eingangstaktsignal abgeleitete Frequenz. Taktverstärker sowie eine entsprechende Verschaltung sorgen dafür, dass jedes verwendete Taktsignal überall im Chip synchron zur Verfügung steht. Moderne FPGAs besitzen typischerweise mehrere Phase-locked loops (PLL), mit denen sich rational gebrochene Taktfrequenzteilungen/-vervielfachungen erzeugen lassen. Den gleichen Zweck erfüllen Delay-locked loops (DLL) und digital frequency synthesizer (DFS), die manche FPGA-Hersteller gegenüber der PLL bereitstellen.

- In vielen FPGAs sind zusätzliche festverdrahtete Funktionen enthalten, wie z. B. Speicherblöcke (sog. Block RAM), die sich in vielfältiger Weise nutzen lassen.

- Für Aufgaben der digitalen Signalverarbeitung sind viele FPGAs zusätzlich zu den normalen Logikzellen mit DSP-Blöcken ausgestattet.[2][3] Diese erlauben, neben der schnellen Multiplikation zweier Zahlen, auch die Verwendung als Multiply-Accumulate-Blöcke, wie sie insbesondere für digitale Filter und andere Faltungsoperationen benötigt werden. Dies ist häufig effizienter, als die zugrundeliegende Funktion aus den universellen Logik-Ressourcen des FPGA zu synthetisieren.

- FPGAs, die aufwändige Berechnungen vollziehen sollen, verfügen über mehrere integrierte Mikrocontroller in Form eines Hard-Cores, welcher z. B. mit einem C-Programm programmiert werden kann.

- FPGAs, die besonders hohe Speicheranforderungen haben, besitzen mehrere integrierte DDR-Controller und neben dem FPGA im gleichen Gehäuse installierte DDR-SDRAM-Blöcke mit mehreren GB Speicherkapazität. Man nennt solche integrierten Schaltungen mit mehreren Chips in einem Gehäuse auch Multi-Die.

- Durch weiteres Hinzufügen von komplexen Funktionsblöcken wie Ethernetschnittstellen, USB-Controllern und DDR-Controllern entstehen System-on-a-Chip-Systeme (SoCs), die den Aufbau vollständiger computerähnlicher Systeme ermöglichen. Die darin verwendeten unveränderlichen Schaltungen belegen sehr viel weniger Chipfläche, als die gleiche Funktion benötigt, wenn sie mit frei konfigurierbaren Logikblöcken realisiert wird. Sie sind auch erheblich stromsparender und um ein Mehrfaches schneller.

- Hersteller wie Xilinx bieten mittlerweile auch FPGAs an, die bereits über im Chipgehäuse untergebrachten Flash-Speicher zur Konfiguration verfügen und keinen externen Flash-Speicher mehr benötigen. Die Lade- bzw. Startzeiten des FPGA bleiben im Vergleich zu externem Speicher in etwa gleich, sind allerdings speziell vom Hersteller optimiert. Ein weiterer Vorteil ist der Schutz vor unrechtmäßigen Kopien durch das Auslesen des extern befindlichen Speichers. Derzeit und auf absehbare Zeit ist es technologisch nicht möglich, die SRAM-basierten Schalterzellen in einem FPGA direkt wie bei den viel einfacheren CPLDs durch Flash- bzw. EEPROM-Zellen zu ersetzen.

Unterschiede zu CPLDs

[Bearbeiten | Quelltext bearbeiten]Oft werden FPGAs mit den digitalen und ebenfalls rekonfigurierbaren CPLD-Bausteinen (Complex Programmable Logic Devices) gleichgesetzt bzw. verglichen. Die wesentlichen Unterschiede zwischen FPGAs und CPLDs sind:

- CPLD gehört noch zur Gruppe der PAL(Programmable Array Logic)/PLA(Programmable Logic Array)/PLD(Programmable Logic Device)/GAL(Generic Array Logic), hat aber einen komplizierteren Innenaufbau im IC als PAL und GAL. Die noch neueren FPGAs gehören hingegen zu einer anderen Technologie[4]. CPLDs weisen im Vergleich zu FPGAs eine wesentlich einfachere Struktur auf. Sie besitzen kein feinmaschiges Array (Feld) von Logikblöcken und Flipflops, sondern nur eine konfigurierbare Schaltmatrix, die verschiedene Eingangssignale zu verschiedenen Ausgangssignalen verbinden kann. Die Signale können dabei durch logische Operationen wie AND/OR verknüpft werden. Dadurch haben CPLDs eine vom jeweiligen Design unabhängige, konstante Signaldurchlaufzeit. Durch entsprechende Designmethoden kann auch bei FPGAs eine definierte maximale Durchlaufzeit erreicht werden (engl. timing constraints).

- CPLDs weisen vergleichsweise wenige Flipflops auf. Vor allem längere Schieberegister, Zähler, Zustandsspeicher und ähnliche Schaltungen, die viele Flipflops benötigen, sind in CPLDs nur ineffizient zu realisieren.

- CPLDs besitzen, da jeder IO-Pin ein Flipflop besitzt, meist sehr viele IO-Pins, die in vielen Anwendungen nur teilweise verwendet werden. In Anwendungen, in denen nur vergleichsweise einfache digitale Schaltungen, sogenannte glue logic, mit einem hohen Bedarf an IO-Pins Verwendung findet, sind CPLDs meist die bessere Wahl.

- CPLDs können durch ihre einfache Struktur technologisch mit Flash-Zellen in den Schaltmatrizen arbeiten. Damit ist ein CPLD sofort nach dem Einschalten (engl. Power-Up) betriebsbereit, während rekonfigurierbare FPGAs mit SRAM-basierenden Zellen erst einen Ladezyklus für die Konfiguration durchlaufen müssen. Von einigen Herstellern gibt es aber seit längerem auch FPGAs in Flash-Technik. Seit Ende der 1990er Jahre ist bei den CPLDs eine Annäherung an die FPGA-SRAM-Technologie zu beobachten. Heute arbeiten die meisten CPLDs intern SRAM-basiert. Bei einigen CPLD-Familien besteht inzwischen das logische Grundelement aus dem FPGA-typischen LUT4-Flipflop-Verbund (Altera MAX II-Serie).

- CPLDs weisen durch den einfacheren Aufbau und die geringere Größe auch einen wesentlich geringeren Stromverbrauch auf.

Konfiguration

[Bearbeiten | Quelltext bearbeiten]Die Programmierung der Logikelemente kann je nach FPGA unterschiedlich gelöst werden. Man kann zwischen Methoden unterscheiden, die es ermöglichen, den FPGA mehrmals zu programmieren, und Methoden, die nur eine einmalige Programmierung zulassen. Bei den mehrmals programmierbaren FPGAs wird die Konfiguration in Speicherzellen (z. B. SRAM, EPROM, EEPROM, Flash) gespeichert. Bei den einmalig programmierbaren FPGAs werden die physikalischen Eigenschaften der Verbindungswege permanent geändert (Antifuse-Technologie). Diese Technologie bietet im Feld eine größere Sicherheit gegen äußere Störungen.

Die Konfiguration der LUTs und der Verbindungsstrukturen bei SRAM-basierten FPGAs erfolgt typischerweise einmal vor jedem Einsatz, wodurch der FPGA auf eine konkrete Funktion festgelegt wird. Das ist notwendig, da der FPGA durch Abschalten der Betriebsspannung seine Konfiguration wieder verliert. Im Einsatz steht dem FPGA deshalb meist eine Art EPROM zur Seite, das die Konfiguration vorhält und dessen Inhalt selbst auch aktualisierbar ist. Der FPGA kann sich selbst aus diesem nichtflüchtigen Speicher beladen. Alternativ kann die Konfiguration auch aktiv durch einen Microcontroller oder einen anderen FPGA erfolgen, der die Konfiguration in den FPGA schreibt.

In der Regel behält der FPGA seine Funktion dann bis zum Abschalten bei. Mehr und mehr wird aber auch eine bereichsweise Umprogrammierung von einzelnen FPGA-Bereichen im laufenden Betrieb unterstützt, um den Platz im FPGA effektiver zu nutzen und eigentlich festverdrahtete Funktionen zu flexibilisieren.

Der Vorgang des Konfigurierens des FPGAs wird oft auch als Programmieren bezeichnet, was jedoch eine begriffliche Überschneidung mit dem Entwurf bedingt.

Entwurfsschritte und -werkzeuge

[Bearbeiten | Quelltext bearbeiten]

Oftmals wird bei der Entwicklung von FPGA-Schaltungen von Programmierung gesprochen. Der Begriff ist in diesem Kontext aber anders zu verstehen, als es von der Erstellung von Software für Prozessoren her bekannt ist. Im Rahmen des Entwicklungsprozesses erfolgt zunächst ein Schaltungsentwurf, gefolgt von einer Prüfung der entstandenen Hardwarebeschreibung mittels Simulationswerkzeugen und dann eine Implementierung (Place and Route) sowie ggf. laufzeitbasierende Simulation. Erst danach kann die implementierte Schaltung am realen FPGA erprobt werden.

Schaltungsentwurf

[Bearbeiten | Quelltext bearbeiten]Erstellt wird die Konfiguration eines FPGA entweder grafisch mittels eines Schaltplans (engl. schematic) oder textuell mit einer Hardwarebeschreibungssprache. Dies sind primär VHDL oder Verilog, welche die gesamte Funktion der Schaltung in Form von Strukturen und Abläufen beschreibt. Die Strukturen und die Verschaltung derselben kann dabei durch Text oder graphische Werkzeuge erfolgen, die ähnlich einem Schaltplaneditor arbeiten. Ein typisches Werkzeug ist der HDL-Designer. Daneben bieten fast alle Hersteller in ihrer tool chain grafische Entwurfswerkzeuge an.

Die im FPGA erforderlichen Ablaufsteuerungen lassen sich durch endliche Automaten darstellen. Der beschreibende Code wird entweder als HDL eingegeben oder ebenfalls mit einem grafischen Entwurfswerkzeug in einem Zwischenschritt automatisch erzeugt.

Darüber hinaus lassen sich mit herstellerunabhängigen grafischen Programmiersystemen wie LabVIEW, Matlab/Simulink oder dem kostenfreien Logiflash[5] Schaltungsmodule und Abläufe für einen FPGA automatisch erstellen.

In den letzten Jahren versuchten mehrere Projekte, Hardwareimplementierungen für ASICs, FPGAs und CPLDs mit der Programmiersprache C (HardwareC, HandelC, BachC) zu beschreiben. Aktuelle Ansätze bauen direkt auf den weit verbreiteten Standardsprachen ANSI C bzw. C++ oder Python (mit MyHDL[6]) auf. Für SystemC existieren keine Synthesetools, der praktische Nutzen für konkrete FPGA-Entwicklungen liegt bei der abstrakten Verhaltensmodellierung und deutlich beschleunigten Systemsimulationen, weshalb es dort zum weitverbreiteten Industriestandard avanciert ist. Es gibt auch High-Level-Synthese-Werkzeuge, um aus Hochsprachen (C/C++, MATLAB, Java, Python, UML) einen Entwurf auf Registertransferebene (VHDL, Verilog) zu erzeugen. Beispiele sind Catapult C Synthesis von Mentor Graphics, CoDeveloper von Impulse Accelerated Technologies, Cynthesizer von Forte Design Systems oder das oben erwähnte freie MyHDL.

Herstellerspezifische Sprachen wie Altera-HDL (AHDL) oder auch die kaum noch verwendete Hardwarebeschreibungssprache ABEL wurden ebenso genutzt wie UDL/I (Japan).

Zur Integration eingebetteter Systeme in FPGAs gibt es Werkzeuge, die eine Konstruktion auf Funktionsblockebene anbieten, z. B. Xilinx EDK (Embedded Development Kit). Funktionsblöcke wie FIFOs, Prozessoren, serielle Schnittstellen, Ethernet-MAC-Layer, RAM-Controller, Parallel-IO etc. werden vom Hersteller zur Verfügung gestellt. Diese Funktionseinheiten, IP-Core genannt, liegen manchmal als Quellcode, oder meist als verschlüsselte Netzliste vor und sind in der Regel parametrierbar (z. B. Baudrate bei seriellen asynchronen Schnittstellen oder Fifo-Tiefe oder Breite der Parallelschnittstelle). Diese werden über Busse mit anderen Funktionseinheiten verbunden.

Für FPGAs wird beim Schaltungsentwurf ein synchrones Schaltungsdesign empfohlen, wenngleich nicht zwingend erforderlich. Das bedeutet: An allen Flipflops in einer sogenannten Takt-Domäne (engl. clock domain) liegt der gleiche Takt. Gesteuert wird die Datenübernahme in ein FPGA-Flipflop am besten nur über die zusätzlich vorhandenen Clock Enable-Eingänge und nicht über geteilte Taktsignale (engl. gated clocks). Das vermeidet schwer handhabbare Laufzeiteffekte. Manche FPGAs bieten spezielle Umschalter an, die das garantiert störungsfreie (glitch-freie) Wechseln zwischen verschiedenen Taktquellen im Betrieb erlauben.

Simulation

[Bearbeiten | Quelltext bearbeiten]

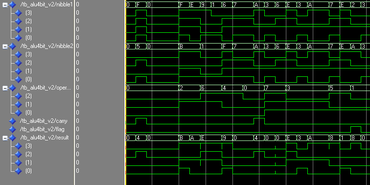

Nach und während der Erstellung der Beschreibung erfolgt regelmäßig eine funktionale Simulation in der Entwicklungssoftware, bei der sichergestellt wird, dass die gewünschten Abläufe eingehalten und alle Elemente korrekt verbunden sind. Die erstellte Hardwarebeschreibung wird dazu wie ein konventionelles Programm interpretiert, compiliert und von einer Simulationssoftware ausgeführt. Dabei handelt es sich entweder um eine interne Komponente der Entwicklungssoftware oder ein externes Programm, wie z. B. ModelSim®.[7] Das Augenmerk liegt bei diesem Schritt hauptsächlich auf der logischen Schaltungsfunktion. Es wird z. B. geprüft, dass Schaltfunktionen unter allen Randbedingungen in der gewünschten Weise ablaufen und Ergebnisse, die in Registern gespeichert werden, zum richtigen Zeitpunkt gelesen und verrechnet werden. Dazu wird für die gesamte Schaltung und bedarfsweise einzelne Module eine Testbench erstellt, welche das Logikdesign mit Daten füttert und unterschiedliche Betriebsfälle abdeckt.

Implementierung und Test

[Bearbeiten | Quelltext bearbeiten]Ausgehend von einer verifizierten Logikschaltung erfolgt dann ein Umsetzen der Netzliste für das konkrete FPGA, wobei auch externe Funktionsblöcke, die von Drittanbietern angeboten werden und bisher nur als black box existierten, eingefügt werden. Ebenso können bei diesem Schritt Teilschaltungen, die zum Testen des FPGAs gedacht sind, wie integrierte Logic Analyzer, hinzugefügt werden. Ein sogenanntes Synthesewerkzeug führt dazu diese Beschreibung wie ein Programm aus und erstellt in mehreren Schritten für den gewünschten Baustein eine spezifische Netzliste unter Nutzung der in diesem Baustein verfügbaren Ressourcen.

Unter Anwendung weiterer Randbedingungen wie Platzierungsanweisungen und Zeitvorgaben, erfolgt dann letztlich das Verteilen der Funktionsblöcke im konkreten FPGA. Nach diesem Schritt können konkrete Annahmen über das Zeitverhalten gemacht werden, welche für besondere Zwecke in einer Simulation geprüft werden können. Vor allem steht nach diesem Schritt fest, ob das vom Programmierer vorgegebene Zeitverhalten eingehalten werden konnte oder ob Änderungen nötig sind. Danach folgt das Umsetzen in ein Programmierfile zum Beladen des FPGAs aus welchem in einem weiteren Schritt ein weiteres Programmierfile erzeugt werden kann, das zum Beladen des Flash-Speichers dient.

Anwendungsbeispiele

[Bearbeiten | Quelltext bearbeiten]FPGAs haben seit ihren Anfängen ihren Anwendungsbereich von der klassischen „Glue-Logic“, also der reinen Verbindungslogik zwischen verschiedenen digitalen Bausteinen, zunehmend erweitert und werden heute auch bei mittleren Stückzahlen für die Realisierung komplexer digitaler Schaltungen bis hin zu kompletten digitalen Systemen eingesetzt. Durch die Rekonfigurierbarkeit von FPGAs direkt beim Endanwender besteht darüber hinaus der wesentliche Vorteil, auf aktuelle technische Entwicklungen reagieren zu können und die digitalen Schaltungen durch Updates anpassen zu können, ohne direkt die zugrundeliegende Hardware der FPGA-Chips verändern zu müssen.

FPGAs werden beispielsweise zur Echtzeit-Verarbeitung von einfachen bis komplexen Algorithmen genutzt, zur digitalen Signalverarbeitung im Rahmen von digitalen Filtern oder zur schnellen Fourier-Transformation. Aber auch Protokoll-Implementierungen wie Teile des Ethernet-MAC-Layers, die Kodierung von digitalen Videosignalen, die Verschlüsselung von Daten und Fehlerkorrekturverfahren sind Anwendungsgebiete.

Besonders in Bereichen, in denen Algorithmen bzw. Protokolle einer schnellen Weiterentwicklung unterliegen, ist die Verwendung rekonfigurierbarer FPGAs statt ASICs angebracht. Die Vorteile sind schnelle Marktreife, die Möglichkeit nachfolgender Fehlerbehebungen, Anpassung an neue Entwicklungen.

Für einige Klassen von Rechenproblemen sind auch FPGA-basierte Parallelcomputer sehr geeignet. Das wahrscheinlich bekannteste Beispiel sind FPGA-Rechner zum Brechen kryptographischer Verfahren, wie dem Data Encryption Standard (DES). Der aus 120 FPGAs bestehende Parallelrechner COPACOBANA ist ein solcher Parallelcomputer zum Codebrechen.

Die inzwischen erreichbare Anzahl von Logikblöcken erlaubt die Integration mehrerer eingebetteter Computersysteme in einen einzigen FPGA-Baustein inklusive CPU(s), Bussystem(en), RAM, ROM, RAM-Controller, Peripherie-Controller etc. Solche kompletten Systeme werden als System-on-a-Chip (SoC) bezeichnet. Auf Grund ihrer Rekonfigurierbarkeit bilden die SRAM- und Flash-basierten FPGAs die Grundlage für rekonfigurierbare Computer.

Digitale Speicheroszilloskope werden oft mit FPGAs realisiert, da deren Stückzahlen meist zu gering sind, um für alle schnellen Komponenten einen ASIC zu entwerfen. Diese verwenden pro Kanal mehrere A/D-Wandler parallel, welche das zu messende Signal phasenverschoben abtasten. Das erfordert ein sehr hohes Maß an paralleler Datenverarbeitung und -speicherung, wofür FPGAs gut geeignet sind. Oszilloskope auf FPGA-Basis können beispielsweise auf sehr kurze Impulse unterhalb der Abtastrate der A/D-Wandler triggern oder diese zählen.

Ein Vorteil bei der Verwendung von FPGAs liegt generell auch darin, dass anders als bei DSPs verhältnismäßig geringe Entwicklungskosten bei Neuentwürfen entstehen, falls einer der verwendeten ICs nicht mehr erhältlich ist und dessen Funktion in einen existenten Baustein integriert werden kann.

FPGAs werden sehr häufig auch als Entwicklungsplattform für den digitalen Teil von ASICs verwendet, um die Funktion zu verifizieren. Das ist nötig, da aufgrund der Komplexität heutiger Schaltungen alleinige Simulationen zu zeitaufwändig wären.

Viele Veröffentlichungen aus unterschiedlichsten Anwendungsgebieten berichten über Migration einer Anwendung von Software nach Configware mit Beschleunigungsfaktoren von einer bis zu vier Größenordnungen. Deshalb finden FPGAs Eingang beim Reconfigurable Computing und beim Ersatz von Mikrocontrollern.

Ein besonders auf FPGA-Entwicklungsysteme zugeschnittener Tochterkartenstandard ist die FPGA Mezzanine Card.

FPGAs kommen auch beim Krypto-Mining zum Einsatz. Dabei werden Kryptowährungen wie beispielsweise Bitcoin, Litecoin, Ethereum oder Monero „geschürft“.[8]

Die Hardwareplattform MiSTer benutzt FPGAs, um eine große Anzahl an älteren Computern, Spielkonsolen und Arcade-Automaten zu simulieren.

Geschichte

[Bearbeiten | Quelltext bearbeiten]Als Field Programmable Gate Array wurden zunächst zu Beginn der 1980er Jahre einfache Anordnungen von Logikgattern bezeichnet, z. B. das 82S150/151 (Signetics, Valvo). Dabei handelte es sich um Schaltungen ohne Flipflops oder Lookup-Tabellen, welche mittels Fuse-Technologie einmalig programmiert werden konnten.[9] FPGAs im heutigen Sinne entwickelten sich Mitte der 1980er Jahre als eigener Teilbereich von Halbleiterbauelementen. Als Vorläufer der FPGAs kann entfernt die schaltungstechnische Kombination von Programmable Read-Only Memory (PROM) und programmierbaren logischen Schaltungen (englisch programmable logic device, PLD) betrachtet werden.[10] Die Kombination von reprogrammierbaren Speicherelementen zur Realisierung von logischen Verknüpfungen in Form eines „Array“ auf einem Halbleiterchip wurde von David Westminster Page und LuVerne R. Peterson 1985 patentiert, aber nicht kommerziell umgesetzt.[11][12]

Der erste kommerziell verfügbare FPGA war der Baustein XC2064, der von Ross Freeman und Bernard Vonderschmitt, beide Gründer des Unternehmens Xilinx, im Jahr 1985 entwickelt wurde.[13] Der XC2064 bestand aus 64 konfigurierbaren Logikblöcken, sogenannten Configurable Logic Blocks (CLBs), mit je einer Lookup-Tabelle (LUT) mit drei Eingängen. Die Logikblöcke waren in einer 8×8-Matrix (Array) angeordnet und konnten über schaltbare Verbindungsleitungen kontaktiert werden. Im Jahr 2009 wurde Freeman für die Entwicklung des ersten FPGAs in die US-amerikanische National Inventors Hall of Fame aufgenommen.[14]

Vergleiche

[Bearbeiten | Quelltext bearbeiten]Mikroprozessoren

[Bearbeiten | Quelltext bearbeiten]FPGAs bilden je nach Konfiguration beliebige Anordnungen digitaler Schaltungsfunktionen ab und bieten damit grundsätzlich die Möglichkeit, Informationen vollkommen parallel zu verarbeiten. So können die anfallenden Datenflüsse in Bandbreite und Informationstiefe optimal einander angepasst werden. Schnell zu erfassende Signale werden dabei oft voll parallel mit Kopien identischer Schaltungsblöcke, langsamer auftretende Signale vermehrt zyklisch mit einer einzigen Schaltung und damit platzsparend verarbeitet.

Externe Prozessoren können dagegen mit wenig Hardware sehr komplexe und verschachtelte Programme sequentiell abarbeiten. Bei einem FPGA müsste für jede Operation ein eigenes Stück Hardware synthetisiert werden, wobei sich die eingeschränkte Anzahl an Logikgattern begrenzend auswirkt, zudem ist der Aufbau einer vergleichbar flexiblen Struktur äußerst schwierig und zeitaufwändig. Daher bedient man sich bei komplexeren Aufgaben einer sogenannten soft core CPU, die in das FPGA-Design eingebunden wird. Diese gleicht den externen CPUs und stellt eine standardisierte Struktur bereit, die in klassischer Weise in C programmiert werden. Heutige FPGAs sind teilweise so leistungsfähig, dass man eine Vielzahl an 8-, 16- oder 32-Bit-CPU-Kernen integrieren kann. Allerdings beanspruchen komplexere CPU-Kerne je nach Konfiguration recht viele Logikressourcen, was sich neben den Kosten in relativ geringer Verarbeitungsleistung verglichen mit Standardprozessoren niederschlägt. Daher gibt es inzwischen FPGAs, die einen oder mehrere hardware-basierte CPU-Kerne enthalten. Nach ersten Anläufen mit ARM-9 (Altera) und PowerPC405 (Xilinx) geht der Trend seit 2010 in Richtung ARM-Cortex-Architektur. Bei Altera und Xilinx haben sich sogenannte SoC-FPGAs mit Dual-Core-Cortex-A9 und fest integrierter Peripherie etabliert. Xilinx bietet in der High-End-Klasse mit der UltraScale-Familie Bausteine an, die zwei CPU-Cluster (QuadCore Cortex-A53 und DualCore Cortex-R5) enthalten. Microsemi hingegen integriert RISC-V Prozessoren (vier Linux-taugliche RV64GC-Kerne und einen RV64IMAC-Kern für Echtzeitanwendungen) in seine Polar-Fire-Familie.

Im Gegensatz zu FPGAs sind Single-Core-Prozessoren reine endliche Zustandsautomaten, die mit einer festgelegten Hardware auskommen müssen und ihr Programm sequentiell abarbeiten, woraus sich auch wesentliche Unterschiede bei der Implementierung von Algorithmen ergeben. Mikroprozessorbausteine beinhalten neben dem eigentlichen Prozessorwerk in der Regel eine feste Peripherie, die direkt genutzt werden kann, und für viele Standardanwendungen ausreichend ist.

Moderne Prozessoren mit SIMD-Befehlen wie zum Beispiel der Intel i7-3930K verarbeiten bis zu 96 Gleitkommabefehle parallel (48 Additionen + 48 Multiplikationen), der erreichbare Durchsatz liegt mit 3,2 GHz bei theoretisch etwa 300 GFlops, von denen 250 GFlops bei praxisrelevanten Aufgaben erreichbar sind. Aktuelle FPGAs können mit Taktfrequenzen von 500 MHz zehntausende Festkommaadditionen (bis 48 bit) und tausende Festkommamultiplikationen (bis 18×25 bit) zur gleichen Zeit ausführen. Damit ist für Aufgaben, die sich mit Festkommaarithmetik bearbeiten lassen, eine um den Faktor 2 bis 3 höhere Verarbeitungsleistung möglich, bei deutlich geringerer Leistungsaufnahme.

Vor- und Nachteile im Vergleich zu anwendungsspezifischen integrierten Schaltungen (ASIC)

[Bearbeiten | Quelltext bearbeiten]Vorteile

[Bearbeiten | Quelltext bearbeiten]- Deutlich geringere Entwicklungskosten (im Gegensatz zu ASICs werden keine Masken mit sehr hohen Fixkosten benötigt).

- bei Prototypen und Kleinserien sehr kostengünstig.

- Dynamisches, applikationsspezifisches Laden unterschiedlicher Hardware-Designs.

- Kürzere Implementierungszeiten.

- Einfach korrigier- und erweiterbar (rekonfigurierbar).

- Geringeres Designrisiko, da es nicht lange vor der Hardwareauslieferung fertig sein muss

- flexible IO-Ports und Standards, d. h. bei technischen Änderungen der Umgebung anpassbar.

Nachteile

[Bearbeiten | Quelltext bearbeiten]- Ab mittleren Stückzahlen höherer Stückpreis (als ASICs).

- Geringere Taktraten (aktuell verfügbar bis 1,5 GHz, typisch werden 20–500 MHz realisiert; digitale ASICs bieten >3 GHz).

- Geringere Logikdichte (ca. 10-facher Flächenbedarf gegenüber ASIC gleicher Technologie).

- Geringere mögliche Komplexität der programmierbaren Logik.

- Deutlich höherer Leistungsbedarf für gleiche Menge an Logik bzw. Funktionen.

- Höhere Empfindlichkeit gegenüber Teilchenstrahlung und elektromagnetischen Wellen (da über RAM-Zellen und nicht durch Hartverdrahtung programmiert).

- Geringere Flexibilität, was Ausstattung z. B. mit eingebettetem Speicher oder analogen Elementen angeht, aber auch bei IO-Buffern.

- Der kürzere Designzyklus und die Möglichkeit, sehr spät noch Fehler korrigieren zu können, verleiten dazu, im Vorfeld weniger funktionale Tests durchzuführen.

- SRAM-basierte FPGAs (das sind z. B. alle von den Marktführern Xilinx und Altera angebotenen) müssen bei jeder Spannungsunterbrechung neu geladen werden. Das bedeutet, dass die Funktionalität nicht direkt nach dem Einschalten zur Verfügung steht. Das Laden kann – je nach eingesetzter Technik – bis zu einigen Sekunden dauern. Handelt es sich nicht um spezielle FPGAs mit integriertem Flashspeicher, sind dazu zusätzliche, externe Komponenten notwendig, z. B. ein herstellerspezifisches EEPROM oder Flash-Speicher, das die Konfiguration enthält oder ein Mikrocontroller mit zusätzlichem Flash-Speicher, der den Ladevorgang durchführt.

Hersteller von FPGAs

[Bearbeiten | Quelltext bearbeiten]- Aeroflex – Strahlungsresistente FPGAs

- Achronix Semiconductor – Sehr schnelle FPGAs (bis 1,5 GHz) in 22 nm

- Abound Logic – Stromsparende FPGAs mit hoher Logikdichte

- Altera (Intel) – seit 1983 FPGA-Produzent. Anbieter eines Migrationspfads vom FPGA MAX10, Cyclone, Arria, Agilex und Stratix bis zu strukturierten ASICs

- Cologne Chip AG – Deutscher Anbieter von Low-Power FPGAs mit neuartiger Architektur.

- Efinix – Anbieter von Low-Power-SRAM-FPGAs mit einzigartiger Quantum-Architektur für geringe Verlustleistung und kleine Gehäuse.

- GOWIN Semiconductor – FPGAs mit geringer Zahl an Logikblöcken, nichtflüchtige und SRAM-basierte, SoC mit Bluetooth

- Lattice – Anbieter eines freien 32 Bit-Open-Source-SoftCore-Prozessors sowie von GAL-Technik. Hat SiliconBlue aufgekauft[15] (Stromsparende FPGAs der iCE Familie)

- Microchip (früher: Atmel & Actel bzw. Microsemi) – FPGAs, auch mit zusätzlich integriertem RAM und AVR-Mikrocontroller

- NanoXplore – Strahlungsresistente FPGAs

- QuickLogic – seit 1988 Anbieter von stromsparenden FPGAs

- Xilinx (seit 2022: AMD) – seit 1984 FPGA-Produzent. Marktführer, bietet das am weitesten ausgebaute SOPC-System, 2022 von AMD übernommen

Siehe auch

[Bearbeiten | Quelltext bearbeiten]- CRUVI FPGA Card FPGA-Tochterkartenstandard

Literatur

[Bearbeiten | Quelltext bearbeiten]- Rajeev Murgai u. a.: Logic Synthesis for Field-Programmable Gate Arrays. Springer, 2012, ISBN 978-1-4613-5994-4.

- Zoran Salcic u. a.: Digital Systems Design and Prototyping Using Field Programmable Logic. Springer, 1997/2013, ISBN 978-1-4613-7807-5.

- Uwe Meyer-Baese: Digital Signal Processing with Field Programmable Gate Arrays (Signals and Communication Technology). 4th Edition, 2014, Springer, ISBN 978-3-642-45308-3.

- Esteban Tlelo Cuautle u. a.: Engineering Applications Of Fpgas (Chaotic Systems, Artificial Neural Networks, Random Number Gener...). Springer, 2016, ISBN 978-3-319-34113-2.

Weblinks

[Bearbeiten | Quelltext bearbeiten]- FPGA-Grundlagen bei mikrocontroller.net

- FAQ von comp.arch.fpga Liste mit häufig gestellten Fragen (englisch)

- FPGA-Datenbank des Unternehmens So-Logic (englisch)

- Zur Einführung von FPGA in den US-Markt auf computerhistory (englisch)

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Martin J. W. Schubert: Praktikumsversuch – Field Programmable Analog Array (FPAA). (PDF; 445 kB) Electronics Laboratory Regensburg University of Applied Sciences, abgerufen am 25. Juli 2020 (englisch).

- ↑ [1] Xilinx User Guide: 7 Series DSP48E1 Slice (PDF, abgerufen am 10. Oktober 2020)

- ↑ [2] Altera Whitepaper: Enabling High-Performance DSP Applications with Stratix Variable-Precision DSP Blocks (PDF, abgerufen am 10. Oktober 2020)

- ↑ Erwin Böhmer/Dietmar Ehrhardt/Wolfgang Oberschelp: Elemente der angewandten Elektronik, Vieweg Verlag Wiesbaden, 2007, 15. Auflage, Anmerkungen zu PAL/PLD/GAL/CPLD S. 418

- ↑ Damm, Klauer, Waldschmidt: LogiFlash. Goethe-Universität Frankfurt am Main, 2018, abgerufen am 21. Juli 2020.

- ↑ MyHDL - open source HDL. MYHDL.ORG, 2020, abgerufen am 21. Juli 2020 (englisch).

- ↑ ModelSim®. Mentor, 2020, abgerufen am 21. Juli 2020 (englisch).

- ↑ Business Wire (dt.): BitHull überholt den ASIC-Markt mit neuen FPGA-Minern. In: wallstreet-online.de. 3. April 2020, abgerufen am 13. Oktober 2020.

- ↑ http://www.bitsavers.org/components/signetics/_dataBooks/1981_Integrated_Fuse_Logic.pdf.pdf Signetics: Integrated Fuse Logic, Nov. 1981 (PDF). bitsavers.org; abgerufen am 4. Okt. 2020

- ↑ History of FPGAs. VT.EDU, 13. Juni 2006, archiviert vom (nicht mehr online verfügbar) am 13. Juni 2007; abgerufen am 11. Juli 2013 (englisch).

- ↑ Patent US4508977: Re-programmable PLA. Veröffentlicht am 2. April 1985, Erfinder: David W. Page, LuVerne R. Peterson.

- ↑ Patent US4524430: Dynamic data re-programmable PLA. Veröffentlicht am 18. Juni 1985, Erfinder: David W. Page.

- ↑ Xilinx, ASIC vendors talk licensing. Abgerufen am 11. Juli 2013.

- ↑ National Inventors Hall of Fame, Ross Freeman. Archiviert vom (nicht mehr online verfügbar) am 25. September 2012; abgerufen am 11. Juli 2013.

- ↑ Lattice Semiconductor Acquires Chipmaker SiliconBlue For $62 Million In Cash. In: TechCrunch. 9. Dezember 2011, abgerufen am 11. April 2019 (englisch).